| Reg | Name:                                                                                                                                                                                                                                                                                         |       |  |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

|     | APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY THIRD SEMESTER B.TECH DEGREE EXAMINATION(S), MAY 2019                                                                                                                                                                                                |       |  |  |  |  |  |  |

|     | Course Code: CS203                                                                                                                                                                                                                                                                            |       |  |  |  |  |  |  |

|     | <b>Course Name: SWITHCING THEORY AND LOGIC DESIGN</b>                                                                                                                                                                                                                                         |       |  |  |  |  |  |  |

| Ma  | x. Marks: 100 Duration: 3 l                                                                                                                                                                                                                                                                   | Hours |  |  |  |  |  |  |

|     | PART A  Answer all questions, each carries 3 marks.                                                                                                                                                                                                                                           | Marks |  |  |  |  |  |  |

| 1   | List out any three advantages of digital systems over analogue systems.                                                                                                                                                                                                                       | (3)   |  |  |  |  |  |  |

| 2   | 2 Do the following number conversions:                                                                                                                                                                                                                                                        |       |  |  |  |  |  |  |

| 3   | (i) base-7 number 3456 to decimal (ii) base-4 number 1213 to binary.  Show the <i>K-map</i> contents for the following Boolean functions: (i) $F(x,y,z) = (x+y)(y+z)$ (ii) $F(x,y,z) = \Pi(0,3,5,7)$ .                                                                                        |       |  |  |  |  |  |  |

| 4   | 4 Use <i>De-Morgan's principle</i> to find the complement of A+BC'(D+EF')'                                                                                                                                                                                                                    |       |  |  |  |  |  |  |

|     | PART B  Answer any two full questions, each carries9 marks.                                                                                                                                                                                                                                   | (7)   |  |  |  |  |  |  |

| 5   | <ul> <li>a) Do the following operations:</li> <li>(i) Compute 1's complement of the binary number 1101.01.</li> <li>(ii) Compute 8's complement of the octal number 672.23.</li> <li>(iii) Add base-16 numbers 1FE and EF1.</li> </ul>                                                        |       |  |  |  |  |  |  |

|     | b) Assume that floating point numbers are represented in the following format. The <i>mantissa</i> is represented in <i>sign-magnitude</i> form. Magnitude of mantissa is adjusted such that the Most significant bit (MSB) is 1 and the (assumed) <i>binary point</i> is to the left of MSB. |       |  |  |  |  |  |  |

|     | Sign bit of Exponent Mantissa Mantissa (1bit) (6 bits signed-2's complement) (9 bits)                                                                                                                                                                                                         |       |  |  |  |  |  |  |

|     | Represent the decimal number 6.25 in binary.                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |

| 6   | Use tabulation method to identify the simplified Boolean expression for the function, $F(w,x,y,z) = \Pi(1,3,4,6,9,11,12,14)$ .                                                                                                                                                                | (9)   |  |  |  |  |  |  |

| 7   | a) Use algebraic manipulation to convert,:<br>(i) $F(x,y,z) = xy+y+z$ into canonical PoS.<br>(ii) $F(x,y,z) = (x+y+z)(x'+y+z)(x+y'+z)$ into standard PoS.                                                                                                                                     | (5)   |  |  |  |  |  |  |

|     | b) Subtract the BCD number 1671 from BCD number 837 using 10's complement addition.                                                                                                                                                                                                           | (4)   |  |  |  |  |  |  |

### **PART C**

# Answer all questions, each carries3 marks.

(3)

(6)

- 8 Show how a *master-slave J-K flip-flop* can be realized using NOR and AND gates. (3)

- 9 Write the truth table of a 4x1 de-multiplexer and show the corresponding logic (3) diagram.

- 10 Show how a *full-subtractor* can be implemented using a decoder. (3)

- 11 Realize a half-adder using NAND gates.

### **PART D**

### Answer any two full questions, each carries 9 marks.

- 12 a) Implement the following Boolean functions using a 2X1 multiplexer and (3) additional gates as needed:  $F(x,y,z) = \sum (1,2,4,5)$ .

- b) Design a code converter with the following mapping specifications:

|             | o-r |     |     |     |     |     |     |     |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Input code  | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| Output code | 001 | 010 | 011 | 100 | 101 | 110 | 111 | 000 |

- 13 a) Given a 2-bit subtractor (block diagram), design a circuit with additional gates (3) to use it as a comparator.

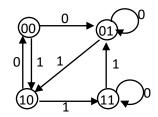

- b) Design a sequential circuit for the following *state diagram* using *T flip-flops*. (6)

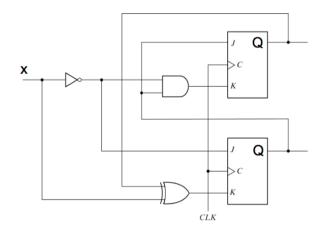

Deduce the *state table* and *state diagram* that represents the behaviour of the (9) following sequential circuit:

### **PART E**

## Answer any four full questions, each carries 10 marks.

- With the help of a neat diagram discuss how a *serial adder* can be designed using (10) full-adder, shift registers and flip-flop.

- Design a *synchronous counter*, using edge-triggered *J-K flip-flops*, that generates (10) the binary sequence: 001, 011, 010, 110, 111, 101, 001, 000, 001, ...

- Draw a *mod-16 ripple up-counter* using J-Kflip-flops. Show how this counter can be converted to a *mod-12 ripple counter*. (10)

- 18 a) How is *static RAM* different from *dynamic RAM*? (3)

- b) Write explanatory notes on *read-only memory* and *read-write memory*. (4)

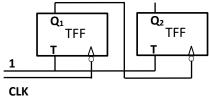

- c) Assuming that both the T flip-flops in the diagram below are initially at state 1, show the *timing diagram* for  $Q_1$  and  $Q_2$  with respect to the *falling edge* of the first four clock pulses.

- 19 a) Write a short note on *PLA*.

- b) Implement the following Boolean functions using a 3-by-4-by-2 PLA. (6)

(4)

- (i)  $F1 = \Sigma(1,4,5,6)$

- (ii)  $F2 = \Sigma (0,2,3,4,6,7)$

- Briefly discuss the algorithms for *floating point addition* and *floating point* (10) subtraction.

\*\*\*\*