**TENTH EDITION**

# **Digital Systems**

**Principles and Applications**

**Ronald J. Tocci**

**Monroe Community College**

**Neal S. Widmer**

**Purdue University**

**Gregory L. Moss**

**Purdue University**

Pearson Education International

If you purchased this book within the United States or Canada you should be aware that it has been wrongfully imported without the approval of the Publisher or the Author.

Director of Development: Vern Anthony Editorial Assistant: Lara Dimmick Production Editor: Stephen C. Robb

Production Coordination: Peggy Hood, TechBooks/GTS

Design Coordinator: Diane Y. Ernsberger

Cover Designer: Jason Moore

Cover Art: Getty One

**Production Manager:** Matt Ottenweller **Marketing Manager:** Ben Leonard

This book was set in TimesEuropa Roman by *TechBooks/GTS* York, PA Campus. It was printed and bound by Courier Kendallville, Inc. The cover was printed by Phoenix Color Corp.

MultiSIM® is a trademark of Electronics Workbench.

Altera is a trademark and service mark of Altera Corporation in the United States and other countries. Altera products are the intellectual property of Altera Corporation and are protected by copyright laws and one or more U.S. and foreign patents and patent applications.

Copyright © 2007 by Pearson Education, Inc., Upper Saddle River, New Jersey 07458. Pearson Prentice Hall. All rights reserved. Printed in the United States of America. This publication is protected by Copyright and permission should be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. For information regarding permission(s), write to: Rights and Permissions Department.

Pearson Prentice Hall<sup>™</sup> is a trademark of Pearson Education, Inc. Pearson® is a registered trademark of Pearson plc Prentice Hall® is a registered trademark of Pearson Education, Inc.

Pearson Education Ltd.

Pearson Education Singapore, Pte. Ltd.

Pearson Education Canada, Ltd.

Pearson Education—Japan

Pearson Education, Upper Saddle River,

New Jersey

Pearson Education Australia Pty. Limited Pearson Education North Asia Ltd. Pearson Educación de Mexico, S.A. de C.V. Pearson Education Malaysia, Pte. Ltd.

10 9 8 7 6 5 4 3 2 1 ISBN: 0-13-173969-7

# **Digital Systems**

## **Principles and Applications**

**TENTH EDITION**

# **Digital Systems**

**Principles and Applications**

**Ronald J. Tocci**

**Monroe Community College**

**Neal S. Widmer**

**Purdue University**

**Gregory L. Moss**

**Purdue University**

Upper Saddle River, New Jersey

Columbus, Ohio

#### Library of Congress Cataloging-in-Publication Data

Tocci, Ronald J.

Digital systems: principles and applications / Ronald J. Tocci, Neal S.

Widmer, Gregory L. Moss.—10th ed.

p. cm.

Includes bibliographical references and index.

ISBN 0-13-172579-3

1. Digital electronics—Textbooks. I. Widmer, Neal S. II. Moss, Gregory L.

III. Title.

TK7868.D5T62 2007 621.381—dc22

2005035835

**Director of Development:** Vern Anthony Editorial Assistant: Lara Dimmick Production Editor: Stephen C. Robb

Production Coordination: Peggy Hood, TechBooks/GTS

Design Coordinator: Diane Y. Ernsberger

Cover Designer: Jason Moore

Cover Art: Getty One

**Production Manager:** Matt Ottenweller Marketing Manager: Ben Leonard

This book was set in TimesEuropa Roman by TechBooks/GTS York, PA Campus. It was printed and bound by Courier Kendallville, Inc. The cover was printed by Phoenix Color Corp.

MultiSIM® is a trademark of Electronics Workbench.

Altera is a trademark and service mark of Altera Corporation in the United States and other countries. Altera products are the intellectual property of Altera Corporation and are protected by copyright laws and one or more U.S. and foreign patents and patent applications.

Copyright © 2007, 2004, 2001, 1998, 1995, 1991, 1988, 1985, 1980, 1970 by Pearson Education, Inc., Upper Saddle River, New Jersey 07458. Pearson Prentice Hall. All rights reserved. Printed in the United States of America. This publication is protected by Copyright and permission should be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. For information regarding permission(s), write to: Rights and Permissions Department.

**Pearson Prentice Hall™** is a trademark of Pearson Education, Inc. Pearson® is a registered trademark of Pearson plc Prentice Hall® is a registered trademark of Pearson Education, Inc.

Pearson Education Ltd. Pearson Education Australia Pty. Limited Pearson Education Singapore, Pte. Ltd. Pearson Education North Asia Ltd. Pearson Education Canada, Ltd. Pearson Educación de Mexico, S.A. de C.V. Pearson Education—Japan Pearson Education Malaysia, Pte. Ltd.

ISBN: 0-13-172579-3

| To you, Cap, for loving me for so long; and for the mil<br>and one ways you brighten the lives of everyone you                                                    |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| To my wife, Kris, and our children, John, Brad, Blake, Matt, and Katie: the lenders of their rights to my tim attention that this revision might be accomplished. |      |

| To my family, Marita, David, and Ryan.                                                                                                                            | —GLM |

This book is a comprehensive study of the principles and techniques of modern digital systems. It teaches the fundamental principles of digital systems and covers thoroughly both traditional and modern methods of applying digital design and development techniques, including how to manage a systems-level project. The book is intended for use in two- and four-year programs in technology, engineering, and computer science. Although a background in basic electronics is helpful, most of the material requires no electronics training. Portions of the text that use electronics concepts can be skipped without adversely affecting the comprehension of the logic principles.

### **General Improvements**

**PREFACE**

The tenth edition of *Digital Systems* reflects the authors' views of the direction of modern digital electronics. In industry today, we see the importance of getting a product to market very quickly. The use of modern design tools, CPLDs, and FPGAs allows engineers to progress from concept to functional silicon very quickly. Microcontrollers have taken over many applications that once were implemented by digital circuits, and DSP has been used to replace many analog circuits. It is amazing that microcontrollers, DSP, and all the necessary glue logic can now be consolidated onto a single FPGA using a hardware description language with advanced development tools. Today's students must be exposed to these modern tools, even in an introductory course. It is every educator's responsibility to find the best way to prepare graduates for the work they will encounter in their professional lives.

The standard SSI and MSI parts that have served as "bricks and mortar" in the building of digital systems for nearly 40 years are now nearing obsolescence. Many of the techniques that have been taught over that time have focused on optimizing circuits that are built from these outmoded devices. The topics that are uniquely suited to applying the old technology but do not contribute to an understanding of the new technology must be removed from

**VIII** PREFACE

the curriculum. From an educational standpoint, however, these small ICs do offer a way to study simple digital circuits, and the wiring of circuits using breadboards is a valuable pedagogic exercise. They help to solidify concepts such as binary inputs and outputs, physical device operation, and practical limitations, using a very simple platform. Consequently, we have chosen to continue to introduce the conceptual descriptions of digital circuits and to offer examples using conventional standard logic parts. For instructors who continue to teach the fundamentals using SSI and MSI circuits, this edition retains those qualities that have made the text so widely accepted in the past. Many hardware design tools even provide an easy-to-use design entry technique that will employ the functionality of conventional standard parts with the flexibility of programmable logic devices. A digital design can be described using a schematic drawing with pre-created building blocks that are equivalent to conventional standard parts, which can be compiled and then programmed directly into a target PLD with the added capability of easily simulating the design within the same development tool.

We believe that graduates will actually apply the concepts presented in this book using higher-level description methods and more complex programmable devices. The major shift in the field is a greater need to understand the description methods, rather than focusing on the architecture of an actual device. Software tools have evolved to the point where there is little need for concern about the inner workings of the hardware but much more need to focus on what goes in, what comes out, and how the designer can describe what the device is supposed to do. We also believe that graduates will be involved with projects using state-of-the-art design tools and hardware solutions.

This book offers a strategic advantage for teaching the vital new topic of hardware description languages to beginners in the digital field. VHDL is undisputedly an industry standard language at this time, but it is also very complex and has a steep learning curve. Beginning students are often discouraged by the rigorous requirements of various data types, and they struggle with understanding edge-triggered events in VHDL. Fortunately, Altera offers AHDL, a less demanding language that uses the same basic concepts as VHDL but is much easier for beginners to master. So, instructors can opt to use AHDL to teach introductory students or VHDL for more advanced classes. This edition offers more than 40 AHDL examples, more than 40 VHDL examples, and many examples of simulation testing. All of these design files are available on the enclosed CD-ROM.

Altera's latest software development system is Quartus II. The MAX+PLUS II software that has been used for many years is still popular in industry and is supported by Altera. Its main drawback is that it does not program the latest devices. The material in this text does not attempt to teach a particular hardware platform or the details of using a software development system. New revisions of software tools appear so frequently that a textbook cannot remain current if it tries to describe all of the details. We have tried to show what this tool can do, rather than train the reader how to use it. However, tutorials have been included on the accompanying CD-ROM that make it easy to learn either software package. The AHDL and VHDL examples are compatible with either Quartus or MAX+PLUS systems. The timing simulations were developed using MAX+PLUS but can also be done with Quartus.

Many laboratory hardware options are available to users of this book. A number of CPLD and FPGA development boards are available for students to use in the laboratory. There are several earlier generation boards similar to Altera's UP2 that contain MAX7000 family CPLDs. A more recent example of an available board is the UP3 board from Altera's university program (see Figure P-1), which contains a larger FPGA from the Cyclone family. An even

Preface

**FIGURE P-1** Altera's UP3 development board.

newer board from Altera is called the DE2 board (see Figure P-2), which has a powerful new 672-pin Cyclone II FPGA and a number of basic features such as switches, LEDs, and displays as well as many additional features for more advanced projects. More development boards are entering the market every year, and many are becoming very affordable. These boards, along with powerful educational software, offer an excellent way to teach and demonstrate the practical implementation of the concepts presented in this text.

The most significant improvements in the tenth edition are found in Chapter 7. Although asynchronous (ripple) counters provide a good introduction to sequential circuits, the real world uses synchronous counter circuits. Chapter 7 and subsequent examples have been rewritten to emphasize synchronous counter ICs and include techniques for analysis, cascading, and using HDL to describe them. A section has also been added to improve the coverage of state machines and the HDL features used to describe them. Other improvements include analysis techniques for combinational circuits, expanded coverage of 555 timer applications, and better coverage of signed binary numbers.

**FIGURE P-2** Altera's DE2 development board.

X Preface

Our approach to HDL and PLDs gives instructors several options:

- 1. The HDL material can be skipped entirely without affecting the continuity of the text.

- 2. HDL can be taught as a separate topic by skipping the material initially and then going back to the last sections of Chapters 3, 4, 5, 6, 7, and 9 and then covering Chapter 10.

- 3. HDL and the use of PLDs can be covered as the course unfolds—chapter by chapter—and woven into the fabric of the lecture/lab experience.

Among all specific hardware description languages, VHDL is clearly the industry standard and is most likely to be used by graduates in their careers. We have always felt that it is a bold proposition, however, to try to teach VHDL in an introductory course. The nature of the syntax, the subtle distinctions in object types, and the higher levels of abstraction can pose obstacles for a beginner. For this reason, we have included Altera's AHDL as the recommended introductory language for freshman courses. We have also included VHDL as the recommended language for more advanced classes or introductory courses offered to more mature students. We do not recommend trying to cover both languages in the same course. Sections of the text that cover the specifics of a language are clearly designated with a color bar in the margin. The HDL code figures are set in a color to match the color-coded text explanation. The reader can focus only on the language of his or her choice and skip the other. Obviously, we have attempted to appeal to the diverse interests of our market, but we believe we have created a book that can be used in multiple courses and will serve as an excellent reference after graduation.

### **Chapter Organization**

It is a rare instructor who uses the chapters of a textbook in the sequence in which they are presented. This book was written so that, for the most part, each chapter builds on previous material, but it is possible to alter the chapter sequence somewhat. The first part of Chapter 6 (arithmetic operations) can be covered right after Chapter 2 (number systems), although this will lead to a long interval before the arithmetic circuits of Chapter 6 are encountered. Much of the material in Chapter 8 (IC characteristics) can be covered earlier (e.g., after Chapter 4 or 5) without creating any serious problems.

This book can be used either in a one-term course or in a two-term sequence. In a one-term course, limits on available class hours might require omitting some topics. Obviously, the choice of deletions will depend on factors such as program or course objectives and student background. A list of sections and chapters that can be deleted with minimal disruption follows:

- Chapter 1: All

- Chapter 2: Section 6

- Chapter 3: Sections 15–20

- Chapter 4: Sections 7, 10–13

- Chapter 5: Sections 3, 23–27

- Chapter 6: Sections 5–7, 11, 13, 16–23

- Chapter 7: Sections 9–14, 21–24

- Chapter 8: Sections 10, 14–19

Preface Xi

• Chapter 9: Sections 5, 9, 15–20

■ Chapter 10: All

Chapter 11: Sections 7, 14–17Chapter 12: Sections 17–21

■ Chapter 13: All

**PROBLEM SETS** This edition includes six categories of problems: basic (B), challenging (C), troubleshooting (T), new (N), design (D), and HDL (H). Undesignated problems are considered to be of intermediate difficulty, between basic and challenging. Problems for which solutions are printed in the back of the text or on the enclosed CD-ROM are marked with an asterisk (see Figure P-3).

**PROJECT MANAGEMENT AND SYSTEM-LEVEL DESIGN** Several real-world examples are included in Chapter 10 to describe the techniques used to manage projects. These applications are generally familiar to most students studying electronics, and the primary example of a digital clock is familiar to everyone. Many texts talk about top-down design, but this text demonstrates the key features of this approach and how to use the modern tools to accomplish it.

**DATA SHEETS** The CD-ROM containing Texas Instruments data sheets that accompanied the ninth edition has been removed. The information that was included on this CD-ROM is now readily available online.

**SIMULATION FILES** This edition also includes simulation files that can be loaded into Electronics Workbench Multisim<sup>®</sup>. The circuit schematics of many of the figures throughout the text have been captured as input files for this popular simulation tool. Each file has some way of demonstrating the operation of the circuit or reinforcing a concept. In many cases, instruments are attached to the circuit and input sequences are applied to demonstrate the concept presented in one of the figures of the text. These circuits can then be modified as desired to expand on topics or create assignments and tutorials

FIGURE P-3 Letters denote categories of problems, and asterisks indicate that corresponding solutions are provided at the end of the text.

#### **PROBLEMS**

#### **SECTION 9-1**

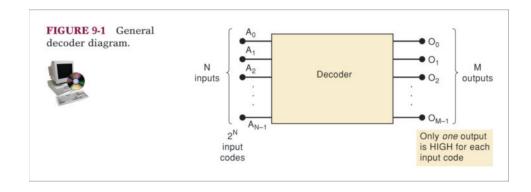

- B 9-1. Refer to Figure 9-3. Determine the levels at each decoder output for the following sets of input conditions.

- (a)\*All inputs LOW

- (b)\*All inputs LOW except  $E_3 = HIGH$

- (c) All inputs HIGH except  $\overline{E}_1 = \overline{E}_2 = \text{LOW}$

- (d) All inputs HIGH

- B 9-2.\*What is the number of inputs and outputs of a decoder that accepts 64 different input combinations?

<sup>\*</sup>Answers to problems marked with an asterisk can be found in the back of the text.

XII PREFACE

FIGURE P-4 The icon denotes a corresponding simulation file on the CD-ROM.

for students. All figures in the text that have a corresponding simulation file on the CD-ROM are identified by the icon shown in Figure P-4.

**IC TECHNOLOGY** This new edition continues the practice begun with the last three editions of giving more prominence to CMOS as the principal IC technology in small- and medium-scale integration applications. This depth of coverage has been accomplished while retaining the substantial coverage of TTL logic.

### **Specific Changes**

The major changes in the topical coverage are listed here.

- Chapter 1. Many explanations covering digital/analog issues have been updated and improved.

- Chapter 2. The octal number system has been removed and the Gray code has been added. A complete standard ASCII code table has been included, along with new examples that relate ASCII characters, hex representation, and computer object code transfer files. New material on framing ASCII characters for asynchronous data transfer has also been added.

- Chapter 3. Along with some new practical examples of logic functions, the major improvement in Chapter 3 is a new analysis technique using tables that evaluate intermediate points in the logic circuit.

- Chapter 4. Very few changes were necessary in Chapter 4.

- Chapter 5. A new section covers digital pulses and associated definitions such as pulse width, period, rise time, and fall time. The terminology used for latch circuit inputs has been changed from Clear to Reset in order to be compatible with Altera component descriptions. The definition of a master/slave flip-flop has been removed as well. The discussion of Schmitt trigger applications has been improved to emphasize their role in eliminating the effects of noise. The inner workings of the 555 timer are now explained, and some improved timing circuits are proposed that make the device more versatile. The HDL coverage of SR and D latches has been rewritten to use a more intuitive behavioral description, and the coverage of counters has been modified to focus on structural techniques to interconnect flip-flop blocks.

- Chapter 6. Signed numbers are covered in more detail in this edition, particularly regarding sign extension in 2's complement numbers and arithmetic overflow. A new calculator hint simplifies negation of binary numbers represented in hex. A number circle model is used to compare

Preface XIII

- signed and unsigned number formats and help students to visualize add/subtract operation using both.

- Chapter 7. This chapter has been heavily revised to emphasize synchronous counter circuits. Simple ripple counters are still introduced to provide a basic understanding of the concept of counting and asynchronous cascading. After examining the limitations of ripple counters in Section 2, synchronous counters are introduced in Section 3 and used in all subsequent examples throughout the text. The IC counters presented are the 74160, '161, '162, and '163. These common devices offer an excellent assortment of features that teach the difference between synchronous and asynchronous control inputs and cascading techniques. The 74190 and '191 are used as an example of a synchronous up/down counter IC, further reinforcing the techniques required for synchronous cascading. A new section is devoted to analysis techniques for synchronous circuits using JK and D flip-flops. Synchronous design techniques now also include the use of D flip-flop registers that best represent the way sequential circuits are implemented in modern PLD technology. The HDL sections have been improved to demonstrate the implementation of synchronous/asynchronous loading, clearing, and cascading. A new emphasis is placed on simulation and testing of HDL modules. State machines are now presented as a topic, the traditional Mealy and Moore models are defined, and a new traffic light control system is presented as an example. Minor improvements have been made in the second half of Chapter 7 also. All of the problems at the end of Chapter 7 have been rewritten to reinforce the concepts.

- Chapter 8. This chapter remains a very technical description of the technology available in standard logic families and digital components. The mixed-voltage interfacing sections have been improved to cover low-voltage technology. The latest Texas Instruments life-cycle curve shows the history and current position of various logic series between introduction and obsolescence. Low-voltage differential signaling (LVDS) is introduced as well.

- Chapter 9. The many different building blocks of digital systems are still covered in this chapter and demonstrated using HDL. Many other HDL techniques, such as tristate outputs and various HDL control structures, are also introduced. A 74ALS148 is described as another example of an encoder. The examples of systems that use counters have all been updated to synchronous operation. The serial transmission system using MUX and DEMUX is particularly improved. The technique of using a MUX to implement SOP expressions has been explained in a more structured way as an independent study exercise in the end-of-the-chapter problems.

- Chapter 10. Chapter 10, which was new to the ninth edition, has remained essentially unchanged.

- Chapter 11. The material on bipolar DACs has been improved, and an example of using DACs as a digital amplitude control for analog waveforms is presented. The more common A/D converter accuracy specification in the form of +/- LSB is explained in this edition.

- Chapter 12. Minor improvements were made to this chapter to consolidate and compress some of the material on older technologies of memory such as UV EPROM. Flash technology is still introduced using a first-generation example, but the more recent improvements, as well as some of the applications of flash technology in modern consumer devices, are described.

- Chapter 13. This chapter, which was new to the ninth edition, has been updated to introduce the new Cyclone family of PLDs.

XIV PREFACE

#### **Retained Features**

This edition retains all of the features that made the previous editions so widely accepted. It utilizes a block diagram approach to teach the basic logic operations without confusing the reader with the details of internal operation. All but the most basic electrical characteristics of the logic ICs are withheld until the reader has a firm understanding of logic principles. In Chapter 8, the reader is introduced to the internal IC circuitry. At that point, the reader can interpret a logic block's input and output characteristics and "fit" it properly into a complete system.

The treatment of each new topic or device typically follows these steps: the principle of operation is introduced; thoroughly explained examples and applications are presented, often using actual ICs; short review questions are posed at the end of the section; and finally, in-depth problems are available at the end of the chapter. These problems, ranging from simple to complex, provide instructors with a wide choice of student assignments. These problems are often intended to reinforce the material without simply repeating the principles. They require students to demonstrate comprehension of the principles by applying them to different situations. This approach also helps students to develop confidence and expand their knowledge of the material.

The material on PLDs and HDLs is distributed throughout the text, with examples that emphasize key features in each application. These topics appear at the end of each chapter, making it easy to relate each topic to the general discussion earlier in the chapter or to address the general discussion separately from the PLD/HDL coverage.

The extensive troubleshooting coverage is spread over Chapters 4 through 12 and includes presentation of troubleshooting principles and techniques, case studies, 25 troubleshooting examples, and 60 *real* troubleshooting problems. When supplemented with hands-on lab exercises, this material can help foster the development of good troubleshooting skills.

The tenth edition offers more than 200 worked-out examples, more than 400 review questions, and more than 450 chapter problems/exercises. Some of these problems are applications that show how the logic devices presented in the chapter are used in a typical microcomputer system. Answers to a majority of the problems immediately follow the Glossary. The Glossary provides concise definitions of all terms in the text that have been highlighted in boldface type.

An IC index is provided at the back of the book to help readers locate easily material on any IC cited or used in the text. The back endsheets provide tables of the most often used Boolean algebra theorems, logic gate summaries, and flip-flop truth tables for quick reference when doing problems or working in the lab.

### **Supplements**

An extensive complement of teaching and learning tools has been developed to accompany this textbook. Each component provides a unique function, and each can be used independently or in conjunction with the others.

**CD-ROM** A CD-ROM is packaged with each copy of the text. It contains the following material:

■ MAX+PLUS<sup>®</sup> II Educational Version software from Altera. This is a fully functional, professional-quality, integrated development environment for

Preface XV

digital systems that has been used for many years and is still supported by Altera. Students can use it to write, compile, and simulate their designs at home before going to the lab. They can use the same software to program and test an Altera CPLD.

- Quartus II Web Version software from Altera. This is the latest development system software from Altera, which offers more advanced features and supports new PLD devices such as the Cyclone family of FPGAs, found on many of the newest educational boards.

- Tutorials. Gregory Moss has developed tutorials that have been used successfully for several years to teach introductory students how to use Altera MAX+PLUS II software. These tutorials are available in PDF and PPT (Microsoft® PowerPoint® presentation) formats and have been adapted to teach Quartus II as well. With the help of these tutorials, anyone can learn to modify and test all the examples presented in this text, as well as develop his or her own designs.

- **Design files from the textbook figures.** More than 40 design files in each language are presented in figures throughout the text. Students can load these into the Altera software and test them.

- Solutions to selected problems: HDL design files. A few of the end-of-chapter problem solutions are available to students. (All of the HDL solutions are available to instructors in the *Instructor's Resource Manual*.) Solutions for Chapter 7 problems include some large graphic and HDL files that are not published in the back of the book but are available on the enclosed CD-ROM.

- Circuits from the text rendered in Multisim<sup>®</sup>. Students can open and work interactively with approximately 100 circuits to increase their understanding of concepts and prepare for laboratory activities. The Multisim circuit files are provided for use by anyone who has Multisim software. Anyone who does not have Multisim software and wishes to purchase it in order to use the circuit files may do so by ordering it from www.prenhall.com/ewb.

- Supplemental material introducing microprocessors and microcontrollers. For the flexibility to serve the diverse needs of the many different schools, an introduction to this topic is presented as a convenient bridge between a digital systems course and an introduction to microprocessors/microcontrollers course.

#### STUDENT RESOURCES

- Lab Manual: A Design Approach. This lab manual, written by Gregory Moss, contains topical units with lab projects that emphasize simulation and design. It utilizes the Altera MAX+PLUS II or Quartus II software in its programmable logic exercises and features both schematic capture and hardware description language techniques. The new edition contains many new projects and examples. (ISBN 0-13-188138-8)

- *Lab Manual: A Troubleshooting Approach.* This manual, written by Jim DeLoach and Frank Ambrosio, is presented with an analysis and troubleshooting approach and is fully updated for this edition of the text. (ISBN 0-13-188136-1)

- Companion Website (www.prenhall.com/tocci). This site offers students a free online study guide with which they can review the material learned in the text and check their understanding of key topics.

**XVI** Preface

#### INSTRUCTOR RESOURCES

- *Instructor's Resource Manual.* This manual contains worked-out solutions for all end-of-chapter problems in this textbook. (ISBN 0-13-172665-X)

- *Lab Solutions Manual.* Worked-out lab results for both lab manuals are featured in this manual. (ISBN 0-13-172664-1)

- **PowerPoint**<sup>®</sup> **presentations.** Figures from the text, in addition to Lecture Notes for each chapter, are available on CD-ROM. (ISBN 0-13-172667-6)

- **TestGen.** A computerized test bank is available on CD-ROM. (ISBN 0-13-172666-8)

To access supplementary materials online, instructors need to request an instructor access code. Go to www.prenhall.com, click the Instructor Resource Center link, and then click Register Today for an instructor access code. Within 48 hours after registering, you will receive a confirming e-mail including an instructor access code. When you have received your code, go to the site and log on for full instructions on downloading the materials you wish to use.

#### **ACKNOWLEDGMENTS**

We are grateful to all those who evaluated the ninth edition and provided answers to an extensive questionnaire: Ali Khabari, Wentworth Institute of Technology; Al Knebel, Monroe Community College; Rex Fisher, Brigham Young University; Alan Niemi, LeTourneau University; and Roger Sash, University of Nebraska. Their comments, critiques, and suggestions were given serious consideration and were invaluable in determining the final form of the tenth edition.

We also are greatly indebted to Professor Frank Ambrosio, Monroe Community College, for his usual high-quality work on the indexes and the *Instructor's Resource Manual*; and Professor Thomas L. Robertson, Purdue University, for providing his magnetic levitation system as an example; and Professors Russ Aubrey and Gene Harding, Purdue University, for their technical review of topics and many suggestions for improvements. We appreciate the cooperation of Mike Phipps and the Altera Corporation for their support in granting permission to use their software package and their figures from technical publications.

A writing project of this magnitude requires conscientious and professional editorial support, and Prentice Hall came through again in typical fashion. We thank the staffs at Prentice Hall and TechBooks/GTS for their help to make this publication a success.

And finally, we want to let our wives and our children know how much we appreciate their support and their understanding. We hope that we can eventually make up for all the hours we spent away from them while we worked on this revision.

Ronald J. Tocci Neal S. Widmer Gregory L. Moss

# BRIEF CONTENTS

| CHAPTER 1         | Introductory Concepts                              | 2   |

|-------------------|----------------------------------------------------|-----|

| CHAPTER 2         | <b>Number Systems and Codes</b>                    | 24  |

| CHAPTER 3         | <b>Describing Logic Circuits</b>                   | 54  |

| <b>CHAPTER 4</b>  | Combinational Logic Circuits                       | 118 |

| <b>CHAPTER 5</b>  | Flip-Flops and Related Devices                     | 208 |

| <b>CHAPTER 6</b>  | <b>Digital Arithmetic: Operations and Circuits</b> | 296 |

| <b>CHAPTER 7</b>  | Counters and Registers                             | 360 |

| <b>CHAPTER 8</b>  | Integrated-Circuit Logic Families                  | 488 |

| <b>CHAPTER 9</b>  | MSI Logic Circuits                                 | 576 |

| <b>CHAPTER 10</b> | Digital System Projects Using HDL                  | 676 |

| <b>CHAPTER 11</b> | Interfacing with the Analog World                  | 718 |

| <b>CHAPTER 12</b> | <b>Memory Devices</b>                              | 786 |

| <b>CHAPTER 13</b> | <b>Programmable Logic Device Architectures</b>     | 868 |

|                   | Glossary                                           | 898 |

|                   | <b>Answers to Selected Problems</b>                | 911 |

|                   | Index of ICs                                       | 919 |

|                   | Index                                              | 922 |

| CHA | APTER 1 Introductory Concepts       | 2  |

|-----|-------------------------------------|----|

| 1-1 | Numerical Representations 4         |    |

| 1-2 | Digital and Analog Systems 5        |    |

| 1-3 | Digital Number Systems 10           |    |

| 1-4 | Representing Binary Quantities 13   |    |

| 1-5 | Digital Circuits/Logic Circuits 15  |    |

| 1-6 | Parallel and Serial Transmission 17 |    |

| 1-7 | Memory 18                           |    |

| 1-8 | Digital Computers 19                |    |

| CHA | APTER 2 Number Systems and Codes    | 24 |

| 2-1 | Binary-to-Decimal Conversions 26    |    |

| 2-2 | Decimal-to-Binary Conversions 26    |    |

| 2-3 | Hexadecimal Number System 29        |    |

| 2-4 | BCD Code 33                         |    |

| 2-5 | The Gray Code 35                    |    |

| 2-6 | Putting It All Together 37          |    |

| 2-7 | The Byte, Nibble, and Word 37       |    |

2-8

2-9

Alphanumeric Codes 39

**2-10** Applications 44

Parity Method for Error Detection 41

**XX** Contents

| Chap | pter 3 Describing Logic Circuits                         | 54  |

|------|----------------------------------------------------------|-----|

| 3-1  | Boolean Constants and Variables 57                       |     |

| 3-2  | Truth Tables 57                                          |     |

| 3-3  | OR Operation with OR Gates 58                            |     |

| 3-4  | AND Operation with AND Gates 62                          |     |

| 3-5  | NOT Operation 65                                         |     |

| 3-6  | Describing Logic Circuits Algebraically 66               |     |

| 3-7  | Evaluating Logic-Circuit Outputs 68                      |     |

| 3-8  | Implementing Circuits from Boolean Expressions 71        |     |

| 3-9  | NOR Gates and NAND Gates 73                              |     |

| 3-10 | Boolean Theorems 76                                      |     |

| 3-11 | DeMorgan's Theorems 80                                   |     |

| 3-12 | Universality of NAND Gates and NOR Gates 83              |     |

| 3-13 | Alternate Logic-Gate Representations 86                  |     |

| 3-14 | Which Gate Representation to Use 89                      |     |

| 3-15 | IEEE/ANSI Standard Logic Symbols 95                      |     |

| 3-16 | Summary of Methods to Describe Logic Circuits 96         |     |

| 3-17 | Description Languages Versus Programming<br>Languages 98 |     |

| 3-18 | Implementing Logic Circuits with PLDs 100                |     |

| 3-19 | HDL Format and Syntax 102                                |     |

| 3-20 | Intermediate Signals 105                                 |     |

| CI.  |                                                          | 440 |

|      | pter 4 Combinational Logic Circuits                      | 118 |

| 4-1  | Sum-of-Products Form 120                                 |     |

| 4-2  | Simplifying Logic Circuits 121                           |     |

| 4-3  | Algebraic Simplification 121                             |     |

| 4-4  | Designing Combinational Logic Circuits 127               |     |

| 4-5  | Karnaugh Map Method 133                                  |     |

| 4-6  | Exclusive-OR and Exclusive-NOR Circuits 144              |     |

| 4-7  | Parity Generator and Checker 149                         |     |

| 4-8  | Enable/Disable Circuits 151                              |     |

| 4-9  | Basic Characteristics of Digital ICs 153                 |     |

| 4-10 | Troubleshooting Digital Systems 160                      |     |

| 4-11 | Internal Digital IC Faults 162                           |     |

| 4-12 | External Faults 166                                      |     |

| 4-13 | Troubleshooting Case Study 168                           |     |

| 4-14 | Programmable Logic Devices 170                           |     |

| 4-15 | Representing Data in HDL 177                             |     |

| 4-16 | Truth Tables Using HDL 181                               |     |

| 4-17 | Decision Control Structures in HDL 184                   |     |

Contents XXI

| Chap         | oter 5 Flip-Flops and Related Devices        | 208 |

|--------------|----------------------------------------------|-----|

| 5-1          | NAND Gate Latch 211                          |     |

| 5-2          | NOR Gate Latch 216                           |     |

| <b>5-3</b>   | Troubleshooting Case Study 219               |     |

| <b>5-4</b>   | Digital Pulses 220                           |     |

| 5-5          | Clock Signals and Clocked Flip-Flops 221     |     |

| <b>5-6</b>   | Clocked S-R Flip-Flop 224                    |     |

| <b>5-7</b>   | Clocked J-K Flip-Flop 227                    |     |

| <b>5-8</b>   | Clocked D Flip-Flop 230                      |     |

| <b>5-9</b>   | D Latch (Transparent Latch) 232              |     |

| <b>5-10</b>  | Asynchronous Inputs 233                      |     |

| 5-11         | IEEE/ANSI Symbols 236                        |     |

| 5-12         | Flip-Flop Timing Considerations 238          |     |

| <b>5-13</b>  | Potential Timing Problem in FF Circuits 241  |     |

| <b>5-14</b>  | Flip-Flop Applications 243                   |     |

| 5-15         | Flip-Flop Synchronization 243                |     |

| <b>5-16</b>  | Detecting an Input Sequence 244              |     |

| <b>5-17</b>  | Data Storage and Transfer 245                |     |

| <b>5-18</b>  | Serial Data Transfer: Shift Registers 247    |     |

| <b>5-19</b>  | Frequency Division and Counting 250          |     |

| <b>5-20</b>  | Microcomputer Application 254                |     |

| 5-21         | Schmitt-Trigger Devices 256                  |     |

| 5-22         | One-Shot (Monostable Multivibrator) 256      |     |

| <b>5-2</b> 3 | Clock Generator Circuits 260                 |     |

| 5-24         | Troubleshooting Flip-Flop Circuits 264       |     |

| 5-25         | Sequential Circuits Using HDL 268            |     |

| <b>5-26</b>  | Edge-Triggered Devices 272                   |     |

| 5-27         | HDL Circuits with Multiple Components 277    |     |

| Chap         | oter 6 Digital Arithmetic:                   |     |

|              | Operations and Circuits                      | 296 |

| 6-1          | Binary Addition 298                          |     |

| 6-2          | Representing Signed Numbers 299              |     |

| 6-3          | Addition in the 2's-Complement System 306    |     |

| 6-4          | Subtraction in the 2's-Complement System 307 |     |

| 6-5          | Multiplication of Binary Numbers 310         |     |

| 6-6          | Binary Division 311                          |     |

| 6-7          | BCD Addition 312                             |     |

| 6-8          | Hexadecimal Arithmetic 314                   |     |

| 6-9          | Arithmetic Circuits 317                      |     |

| 6-10         | Parallel Binary Adder 318                    |     |

| 6-11         | Design of a Full Adder 320                   |     |

**XXII** CONTENTS

| 6-12         | Complete Parallel Adder with Registers 323        |     |

|--------------|---------------------------------------------------|-----|

| 6-13         | Carry Propagation 325                             |     |

| 6-14         | Integrated-Circuit Parallel Adder 326             |     |

| 6-15         | 2's-Complement System 328                         |     |

| 6-16         | ALU Integrated Circuits 331                       |     |

| 6-17         | Troubleshooting Case Study 335                    |     |

| 6-18         | Using TTL Library Functions with HDL 337          |     |

| 6-19         | Logical Operations on Bit Arrays 338              |     |

| 6-20         | HDL Adders 340                                    |     |

| 6-21         | Expanding the Bit Capacity of a Circuit 343       |     |

| Chap         | oter 7 Counters and Registers                     | 360 |

| 7-1          | Asynchronous (Ripple) Counters 362                |     |

| 7-2          | Propagation Delay in Ripple Counters 365          |     |

| <b>7-3</b>   | Synchronous (Parallel) Counters 367               |     |

| <b>7-4</b>   | Counters with MOD Numbers $<2^N$ 370              |     |

| 7-5          | Synchronous Down and Up/Down Counters 377         |     |

| 7-6          | Presettable Counters 379                          |     |

| 7-7          | IC Synchronous Counters 380                       |     |

| 7-8          | Decoding a Counter 389                            |     |

| 7-9          | Analyzing Synchronous Counters 393                |     |

| <b>7-10</b>  | Synchronous Counter Design 396                    |     |

| 7-11         | Basic Counters Using HDLs 405                     |     |

| 7-12         | Full-Featured Counters in HDL 412                 |     |

| <b>7-13</b>  | Wiring HDL Modules Together 417                   |     |

| <b>7-14</b>  | State Machines 425                                |     |

| 7-15         | Integrated-Circuit Registers 437                  |     |

| <b>7-16</b>  | Parallel In/Parallel Out—The 74ALS174/74HC174 437 |     |

| 7-17         | Serial In/Serial Out—The 74ALS166/74HC166 439     |     |

| <b>7-18</b>  | Parallel In/Serial Out—The 74ALS165/74HC165 441   |     |

| <b>7-19</b>  | Serial In/Parallel Out—The 74ALS164/74HC164 443   |     |

| <b>7-20</b>  | Shift-Register Counters 445                       |     |

| <b>7-21</b>  | Troubleshooting 450                               |     |

| 7-22         | HDL Registers 452                                 |     |

| <b>7-2</b> 3 | HDL Ring Counters 459                             |     |

| 7-24         | HDL One-Shots 461                                 |     |

| Chap         | oter 8 Integrated-Circuit Logic Families          | 488 |

| 8-1          | Digital IC Terminology 490                        |     |

| 8-2          | The TTL Logic Family 498                          |     |

| 8-3          | TTL Data Sheets 502                               |     |

| 8-4          | TTL Series Characteristics 506                    |     |

|              |                                                   |     |

Contents **xxiii**

| 10-1         | Small-Project Management 678                                                   |     |

|--------------|--------------------------------------------------------------------------------|-----|

| Chap         | oter 10 Digital System Projects Using HDL                                      | 676 |

| J-20         | TIDE Code Converters 033                                                       |     |

| 9-20         | HDL Code Converters 653                                                        |     |

| 9-19         | HDL Magnitude Comparators 652                                                  |     |

| 9-18         | HDL Multiplexers and Demultiplexers 648                                        |     |

| 9-17         | Encoders Using HDL 645                                                         |     |

| 9-16         | The HDL 7-Segment Decoder/Driver 642                                           |     |

| 9-14         | Decoders Using HDL 638                                                         |     |

| 9-13<br>9-14 | Data Bus Operation 632                                                         |     |

| 9-12<br>9-13 | The 74ALS173/HC173 Tristate Register 629                                       |     |

| 9-11         | Data Busing 628                                                                |     |

| 9-10         | Code Converters 624                                                            |     |

| 9-9          | Magnitude Comparator 621                                                       |     |

| 9-9          | More Troubleshooting 617                                                       |     |

| 9-7<br>9-8   | Demultiplexers (Data Distributors) 610                                         |     |

| 9-6<br>9-7   | Multiplexers (Data Selectors) 599 Multiplexer Applications 604                 |     |

| 9-5          | Troubleshooting 597  Multipleyers (Pata Selectors) 599                         |     |

| 9-4          | Encoders 591 Troubleshooting 597                                               |     |

| 9-3          | Liquid-Crystal Displays 587                                                    |     |

| 9-2          | BCD-to-7-Segment Decoder/Drivers 584                                           |     |

| 9-1          | Decoders 577  PCD to 7 Segment Decoder/Drivers 584                             |     |

|              | oter 9 MSI Logic Circuits                                                      | 576 |

| 0-13         | Troubleshooting 556                                                            |     |

| 8-19         | Troubleshooting 556                                                            |     |

| 8-17         | Analog Voltage Comparators 554                                                 |     |

| 8-17         | Mixed-Voltage Interfacing 553                                                  |     |

| 8-16         | IC Interfacing 548                                                             |     |

| 8-15         | CMOS Transmission Gate (Bilateral Switch) 546                                  |     |

| 8-14         | The ECL Digital IC Family 543                                                  |     |

| 8-12<br>8-13 | High-Speed Bus Interface Logic 541                                             |     |

| 8-11<br>8-12 | Open-Collector/Open-Drain Outputs 533 Tristate (Three-State) Logic Outputs 538 |     |

| 8-10         | Low-Voltage Technology 530                                                     |     |

| 8-9          | CMOS Series Characteristics 523                                                |     |

| 8-8          | Complementary MOS Logic 521                                                    |     |

| 8-7          | MOS Technology 518                                                             |     |

| 8-6          | Other TTL Characteristics 514                                                  |     |

| 8-5          | TTL Loading and Fan-Out 509                                                    |     |

|              |                                                                                |     |

10-2

Stepper Motor Driver Project 679

10-3 Keypad Encoder Project 687

**XXIV** CONTENTS

| 10-5                                                                                                                          | Frequency Counter Project 710                                                                                                                                                                                                                                                                                                                                                 |     |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                               |     |

| Chap                                                                                                                          | ter 11 Interfacing with the Analog World                                                                                                                                                                                                                                                                                                                                      | 718 |

| 11-1                                                                                                                          | Review of Digital Versus Analog 719                                                                                                                                                                                                                                                                                                                                           |     |

| 11-2                                                                                                                          | Digital-to-Analog Conversion 721                                                                                                                                                                                                                                                                                                                                              |     |

| 11-3                                                                                                                          | D/A-Converter Circuitry 728                                                                                                                                                                                                                                                                                                                                                   |     |

| 11-4                                                                                                                          | DAC Specifications 733                                                                                                                                                                                                                                                                                                                                                        |     |

| 11-5                                                                                                                          | An Integrated-Circuit DAC 735                                                                                                                                                                                                                                                                                                                                                 |     |

| 11-6                                                                                                                          | DAC Applications 736                                                                                                                                                                                                                                                                                                                                                          |     |

| 11-7                                                                                                                          | Troubleshooting DACs 738                                                                                                                                                                                                                                                                                                                                                      |     |

| 11-8                                                                                                                          | Analog-to-Digital Conversion 739                                                                                                                                                                                                                                                                                                                                              |     |

| 11-9                                                                                                                          | Digital-Ramp ADC 740                                                                                                                                                                                                                                                                                                                                                          |     |

| <b>11-10</b>                                                                                                                  | Data Acquisition 745                                                                                                                                                                                                                                                                                                                                                          |     |

| 11-11                                                                                                                         | Successive-Approximation ADC 749                                                                                                                                                                                                                                                                                                                                              |     |

| 11-12                                                                                                                         | Flash ADCs 755                                                                                                                                                                                                                                                                                                                                                                |     |

| 11-13                                                                                                                         | Other A/D Conversion Methods 757                                                                                                                                                                                                                                                                                                                                              |     |

| 11-14                                                                                                                         | Sample-and-Hold Circuits 761                                                                                                                                                                                                                                                                                                                                                  |     |

| <b>11-15</b>                                                                                                                  | Multiplexing 762                                                                                                                                                                                                                                                                                                                                                              |     |

| <b>11-16</b>                                                                                                                  | Digital Storage Oscilloscope 764                                                                                                                                                                                                                                                                                                                                              |     |

| <b>11-17</b>                                                                                                                  | Digital Signal Processing (DSP) 765                                                                                                                                                                                                                                                                                                                                           |     |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                               |     |

| Chan                                                                                                                          | ter 12 Memory Devices                                                                                                                                                                                                                                                                                                                                                         | 784 |

| 12-1                                                                                                                          | 101 12 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                      | 70. |

| 12-1                                                                                                                          | Momory Torminology 786                                                                                                                                                                                                                                                                                                                                                        |     |

| 12-2                                                                                                                          | Memory Terminology 786                                                                                                                                                                                                                                                                                                                                                        |     |

|                                                                                                                               | General Memory Operation 790                                                                                                                                                                                                                                                                                                                                                  |     |

|                                                                                                                               | General Memory Operation 790 CPU–Memory Connections 793                                                                                                                                                                                                                                                                                                                       |     |

| 12-4                                                                                                                          | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795                                                                                                                                                                                                                                                                                                |     |

| 12-4<br>12-5                                                                                                                  | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796                                                                                                                                                                                                                                                                           |     |

| 12-4<br>12-5<br>12-6                                                                                                          | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799                                                                                                                                                                                                                                                            |     |

| 12-4<br>12-5<br>12-6<br>12-7                                                                                                  | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800                                                                                                                                                                                                                                          |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8                                                                                          | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808                                                                                                                                                                                                                         |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9                                                                                  | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811                                                                                                                                                                                                    |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10                                                                         | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814                                                                                                                                                                              |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11                                                                | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815                                                                                                                                                         |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12                                                       | General Memory Operation 790 CPU–Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818                                                                                                                                   |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13                                              | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823                                                                                                            |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14                                     | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823 Dynamic RAM Structure and Operation 824                                                                    |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14<br>12-15                            | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823 Dynamic RAM Structure and Operation 824 DRAM Read/Write Cycles 829                                         |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14<br>12-15<br>12-16                   | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823 Dynamic RAM Structure and Operation 824 DRAM Read/Write Cycles 829 DRAM Refreshing 831                     |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14<br>12-15<br>12-16<br>12-17          | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823 Dynamic RAM Structure and Operation 824 DRAM Read/Write Cycles 829 DRAM Refreshing 831 DRAM Technology 834 |     |

| 12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14<br>12-15<br>12-16<br>12-17<br>12-18 | General Memory Operation 790 CPU-Memory Connections 793 Read-Only Memories 795 ROM Architecture 796 ROM Timing 799 Types of ROMs 800 Flash Memory 808 ROM Applications 811 Semiconductor RAM 814 RAM Architecture 815 Static RAM (SRAM) 818 Dynamic RAM (DRAM) 823 Dynamic RAM Structure and Operation 824 DRAM Read/Write Cycles 829 DRAM Refreshing 831                     |     |

CONTENTS

12-20 Troubleshooting RAM Systems 847

**12-21** Testing ROM 852

| Chap  | ter 13 Programmable Logic Device       |     |

|-------|----------------------------------------|-----|

|       | Architectures                          | 868 |

| 13-1  | Digital Systems Family Tree 870        |     |

| 13-2  | Fundamentals of PLD Circuitry 875      |     |

| 13-3  | PLD Architectures 877                  |     |

| 13-4  | The GAL 16V8 (Generic Array Logic) 881 |     |

| 13-5  | The Altera EPM7128S CPLD 885           |     |

| 13-6  | The Altera FLEX10K Family 890          |     |

| 13-7  | The Altera Cyclone Family 894          |     |

| Gloss | ary 898                                |     |

| Answ  | ers to Selected Problems 911           |     |

| Index | of ICs 919                             |     |

| Index | 922                                    |     |